Programming a XC9572XL

It all started with a simple question by Tom from Numato Labs: “did you check whether the provided oscillator on the breakout works?”. So I took out my DMM and started measuring. And I got - nothing. After changing the jumper I got at least a reading for the 20 MHz setting (it showed 20.49 MHz). It turns out that my meter is only rated up to 8 MHz. So I went ahead and thought: Since I have a CPLD connected to the oscillator, why not just put some frequency divider (aka counters) on it and measure just the lower frequencies? And so did the journey begin into the land of CPLD programming…

First of all: Xilinx ISE WebPack 12.2 doesn’t really like my Kubuntu 11.10. It often complains about missing shared libraries (libxul and libxpcom). But the main features work, just some tools don’t load.

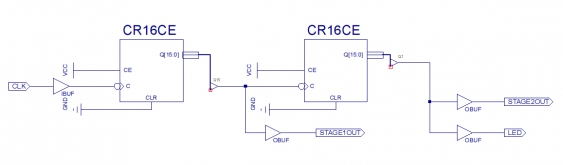

So I fired up the schematics editor, since I didn’t want to learn Verilog or VHDL right now for such a simple thing. It turns out there are many counter components to be used - from 2 up to 16 stages, with load or without, synchronous, ripple or Johnson-style, binary vs. BCD and some other differences. So I did choose the 4bit BCD counter (CD4CE), since it would allow to divide in multiple stages by 10, down to 2 Hz (which I then would connect to one of the LEDs). Unfortunately, the data sheet for this component is s little bit unclear on how to cascade multiple counter together: “Larger counters are created by connecting the count enable out (CEO) output of the first stage to the CE input of the next stage and connecting the CLR and clock inputs in parallel.” In the end it means connect all clock inputs together to the cock input, and all reset lines together (to GND if unused). But I didn’t figure out this until later on, and so got only the first stage to work (but at least this allowed me to check that the frequency of the oscillator is indeed 20.49 MHz, meaning a 2.5% deviation which is OK for a R-controlled one). And since I wanted to get it going, I switched to a ripple (asynchronous) counter.

But even before that, there were some other obstacles to overcome - there are several thing one can easily overlook. For a beginning, Vio on the CPLD needs to be connected for the programming to work. This is only stated deeply hidden in the XC9572XL data sheet, and can be difficult to find out. Oh and btw. the Vio voltage should be 3.3 volts - but I measured 2.0V. Culprit was the jumper I used for connecting Vio - it gave some kind of connection, but not enough (moving it changed the voltage, so it was kind of nondeterministic when the programming failed). Aargh!

Next one is to power-cycle the CPLD after programming. One can get it into programming mode from whatever it is doing (which e.g. disables all outputs) but it won’t load its new code afterwards).

What was even more mysterious: I couldn’t get the example from DP to work. I drew the schematics, wrote the constraints file, programmed the CPLD - and nothing happens. Thats the most terrible thing which can happen, especially since there is not really a debugger for that one (OK, if I would have a proper JTAG cable I could do a boundary scan…). The reason here? The XC9572XL comes in two different 44 pin packages (PLCC and VQFP), which have a completely different pin layout. And I surely chose the wrong one (PC44), and so all my signals got routed to the wrong pins.

Apart from all these findings (which took me about 4 hours on two evenings to figure out) it worked quite fine. One needs to remember to add buffers for all IO signals (see schematic above). If the solution can be expressed in terms of standard logic, using a schematic seems quite a good way. But I’m sure for more complex problems using a HDL is easier, because then the CPLD software can figure out how to express it in hardware.

I also found a somewhat efficient way to generate XSVF files. When you compile the schematic, a corresponding JED file is created from it. I open up the iMPACT tool once, create a new project and the add this JED file as configuration file. This shows a XC9572XL device in the project. I then right-click on it and do a “quick-generate XSVF file”, which creates a file “autoproject.xsvf”. Whenever I recompile my schematic, iMPACT asks me to reload the JED file before creating the XSVF file. Next to doing everything as shell script, this works quite fast (just 2 clicks per run). And it is the CPLD programming which is the slow part…